# 1985 DATA BOOK

**Rockwell International**

**Semiconductor Products Division**

Rockwell Semiconductor Products Division is headquartered in Newport Beach, California with Field Sales Offices located throughout the United States, Canada Europe and the Far East. Their listings, plus those of domestic and international representatives and distributors, appear on pages A-1 through A-5 of this publication.

### NOTICE

Rockwell International does not assume any liability arising out of the application or use of any products, circuit or software described herein, neither does it convey any license under its patent rights nor the patent rights of others. Rockwell International further reserves the right to make changes in any products described herein without notice. Specifications in the Data Book are subject to change without notice. Preliminary specifications have tentative parameters which may be subject to change after final product characterization is completed.

### **TABLE OF CONTENTS**

| Ro  | ckwell Semiconductor Cross-Reference            |       |   | R65C02 CMOS Microprocessor (CPU)                                 | 2-226 |

|-----|-------------------------------------------------|-------|---|------------------------------------------------------------------|-------|

| (   | Guide                                           | 1     |   | R65C102 CMOS Microprocessor (CPU)                                |       |

|     |                                                 |       |   | R65C112 CMOS Microprocessor (CPU)                                |       |

| Αp  | plication Note Index                            | 2     |   | R65C21 CMOS Peripheral Interface Adapter (PIA).                  |       |

| Pa  | rt Number/Data Book Page Index                  | 3     |   | R65C22 Versatile Interface Adapter (VIA)                         | 2-254 |

|     |                                                 |       |   | (PIAT)                                                           | 2-276 |

| ind | lex by Product Family                           | 5     |   | R65C51 CMOS Asynchronous Communications Interface Adapter (ACIA) | 2-296 |

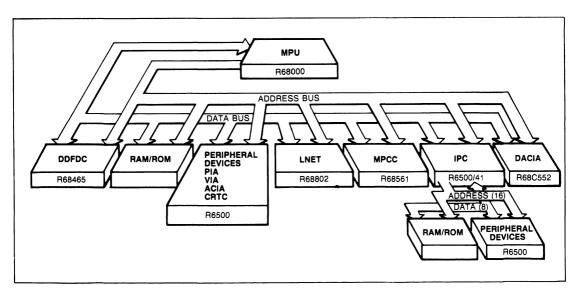

| 1   | R68000 Microprocessor and Peripherals           | 1-1   |   | R65C52 CMOS Dual Asynchronous                                    |       |

|     | Product Family Overview                         | 1-1   |   | Communications Interface Adapter (DACIA)                         | 2-316 |

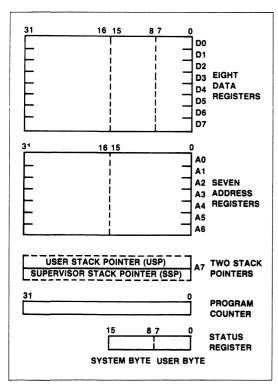

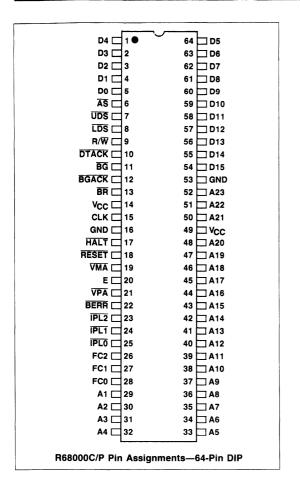

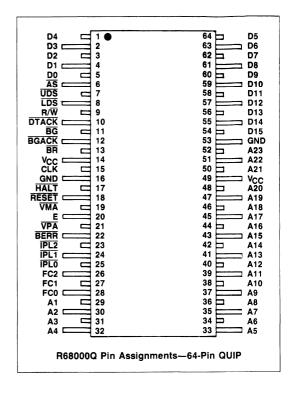

|     | R68000 16-Bit Microprocessing Unit (MPU)        | 1-3   |   | Z80/8080 Bus Compatible Products                                 |       |

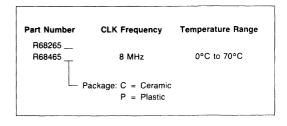

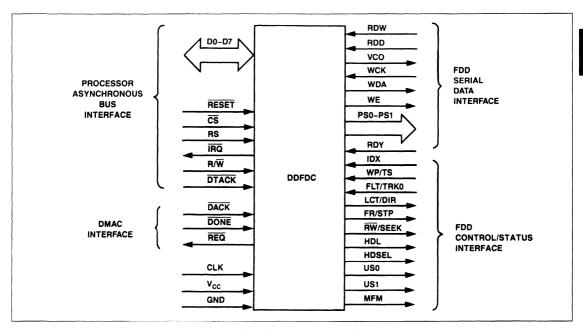

|     | R68265 Double-Density Floppy Disk Controller    |       |   | R6265 Double-Density Floppy Disk Controller                      |       |

|     | (DDFDC)                                         | 1-60  |   | (DDFDC)                                                          | 2-335 |

|     | R68465 Double-Density Floppy Disk Controller    |       |   | R6765 Double-Density Floppy Disk Controller                      |       |

|     | (DDFDC)                                         | 1-60  |   | (DDFDC)                                                          | 2-335 |

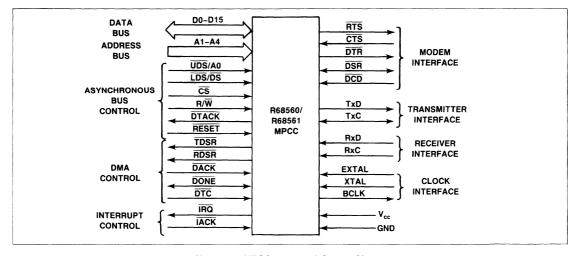

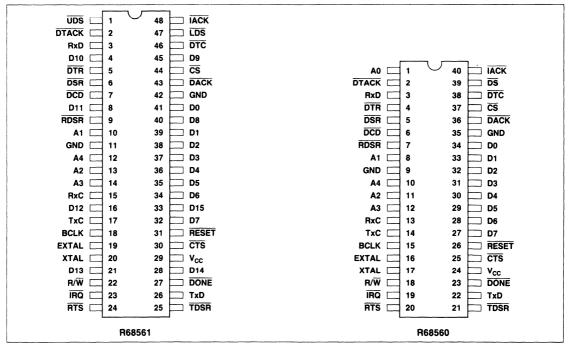

|     | R68560 Multi-Protocol Communications Controller |       |   |                                                                  |       |

|     | (MPCC)                                          | 1-86  |   |                                                                  |       |

|     | R68561 Multi-Protocol Communications Controller |       |   |                                                                  |       |

|     | (MPCC)                                          | 1-86  | 3 | R6500/* Microcomputers                                           | 3-1   |

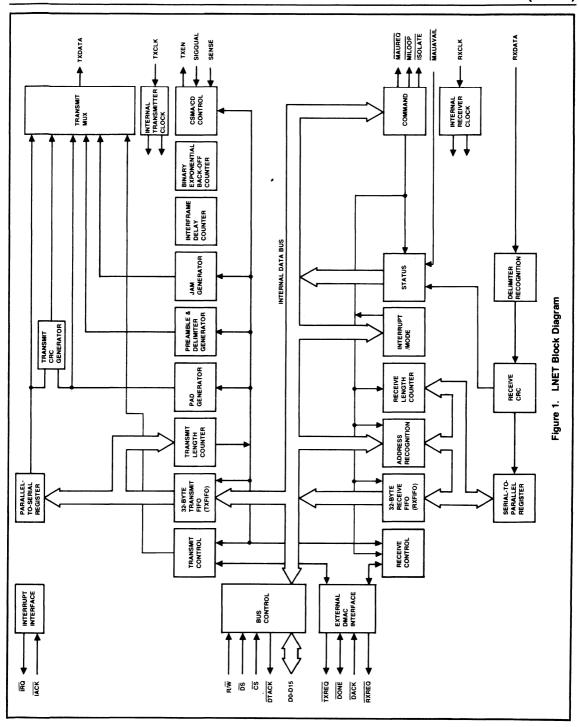

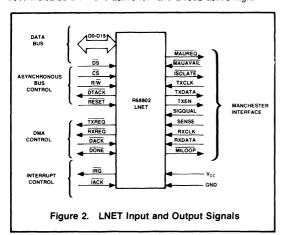

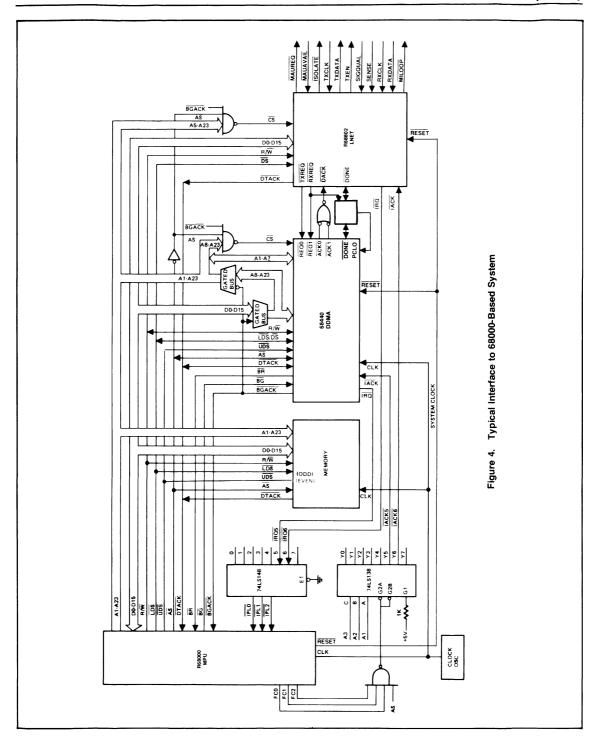

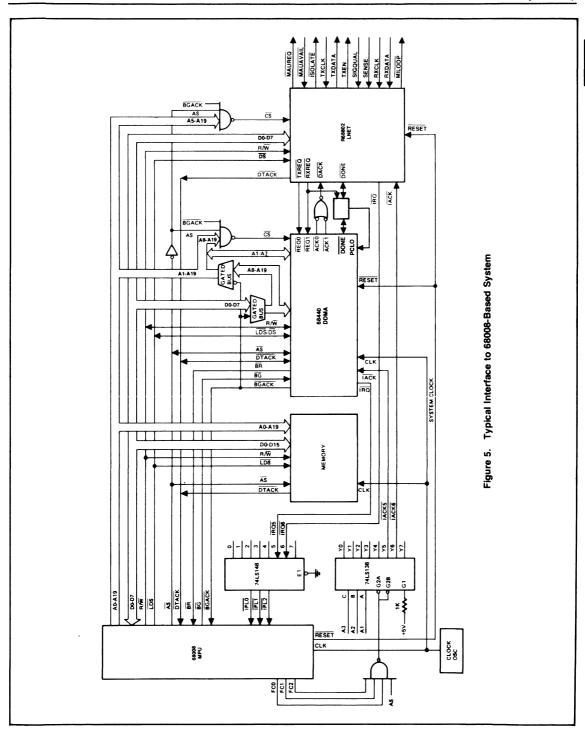

|     | R68802 Local Network Controller (LNET)          | 1-118 |   | Product Family Overview                                          | 3-2   |

|     | R68C552 Dual Asynchronous Communications        |       |   | R65C00/21 Dual CMOS Microcomputer                                | 3-3   |

|     | Interface Adapter (DACIA)                       | 1-138 |   | R65C29 Dual CMOS Microprocessor                                  | 3-3   |

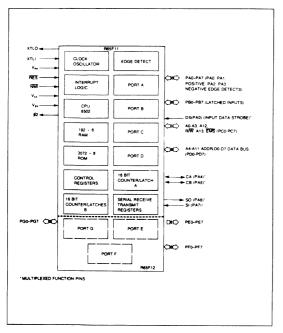

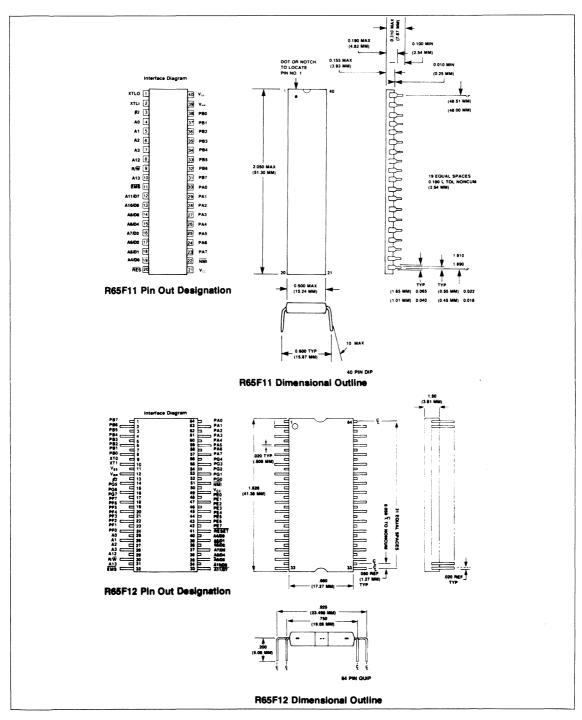

|     |                                                 |       |   | R65F11 FORTH One-Chip Microcomputer                              | 3-36  |

| 2   | 8-Bit Microprocessors and Peripherals           | 2-1   |   | R65F12 FORTH One-Chip Microcomputer                              | 3-36  |

|     | Product Family Overview                         | 2-2   |   | R65FRX RSC FORTH Development and Kernel                          |       |

|     | R6500 Family Products                           |       |   | ROMs                                                             | 3-68  |

|     | R650X Microprocessors (CPU)                     | 2-3   |   | R65FKX RSC FORTH Development and Kernel                          |       |

|     | R651X Microprocessors (CPU)                     |       |   | ROMs                                                             | 3-68  |

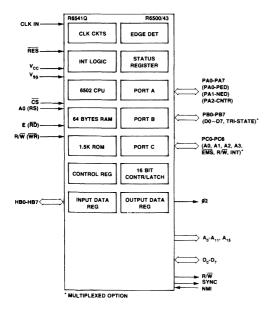

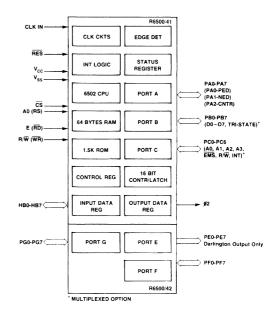

|     | R6501Q One-Chip Microprocessor                  |       |   | R6501Q One-Chip Microprocessor                                   | 3-76  |

|     | R6511Q One-Chip Microprocessor                  |       |   | R6500/1 One-Chip Microcomputer                                   |       |

|     | R6520 Peripheral Interface Adapter (PIA)        |       |   | R6500/1E Emulator Device                                         |       |

|     | R6522 Versatile Interface Adapter (VIA)         |       |   | R6500/1EB Backpack Emulator                                      |       |

|     | R6530 ROM-RAM-I/O Timer (RRIOT)                 |       |   | R6500/1EAB Backpack Emulator                                     |       |

|     | R6531 ROM-RAM-I/O-Counter (RRIOC)               |       |   | R6500/11 One-Chip Microcomputer                                  |       |

|     | R6532 RAM-I/O-Timer (RIOT)                      | 2-82  |   | R6500/12 One-Chip Microcomputer                                  |       |

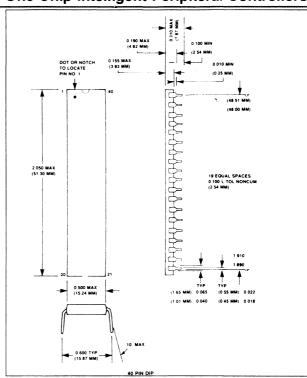

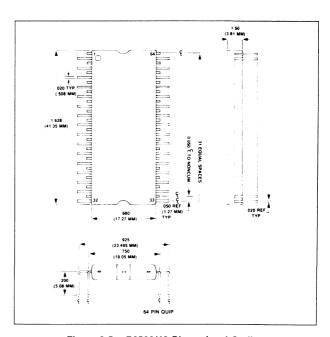

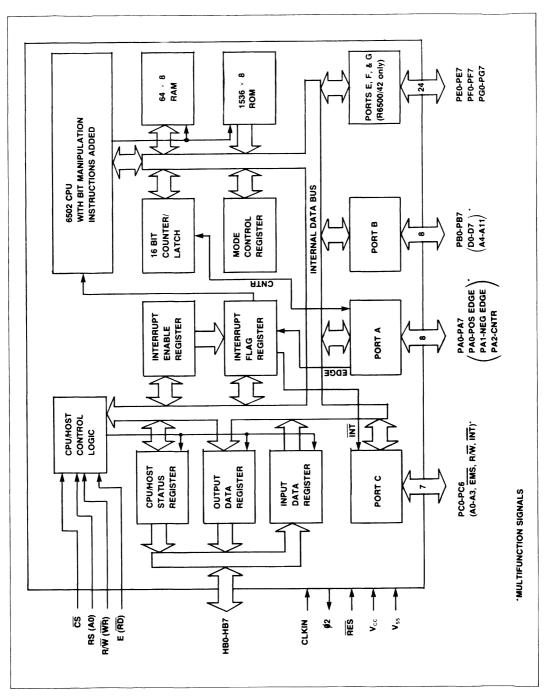

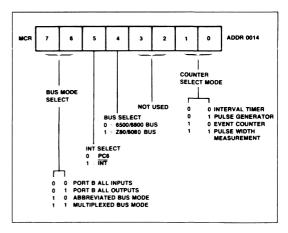

|     | R6541Q One-Chip Intelligent Peripheral          |       |   | R6500/15 One-Chip Microcomputer                                  |       |

|     | Controller                                      | 2-92  |   | R6500/16 One-Chip Microcomputer                                  |       |

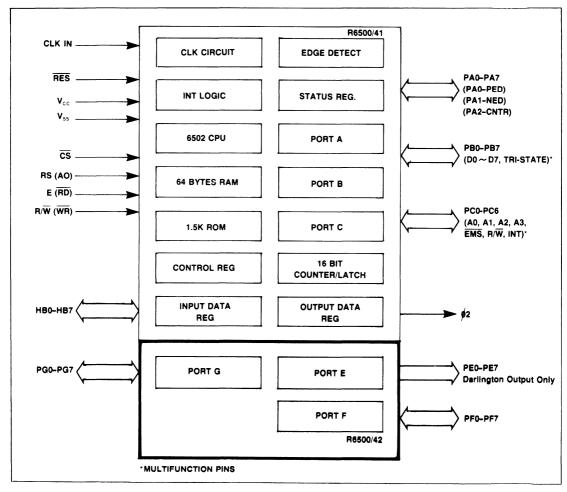

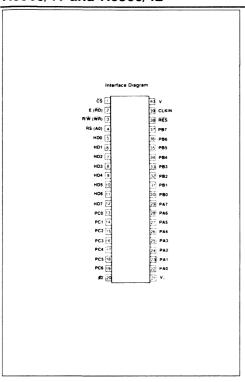

|     | R6500/41 One-Chip Intelligent Peripheral        |       |   | R65/11EB Backpack Emulator                                       |       |

|     | Controller                                      | 2-92  |   | R65/11EAB Backpack Emulator                                      |       |

|     | R6500/42 One-Chip Intelligent Peripheral        |       |   | R6511Q One-Chip Microprocessor                                   |       |

|     | Controller                                      | 2-92  |   | R6500/13 One-Chip Microcomputer                                  | 3-189 |

|     | R6500/43 One-Chip Intelligent Peripheral        |       |   | R6500/41 One-Chip Intelligent Peripheral                         |       |

|     | Controller                                      |       |   | Controller                                                       | 3-224 |

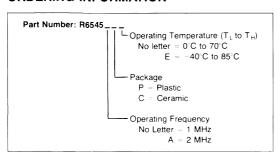

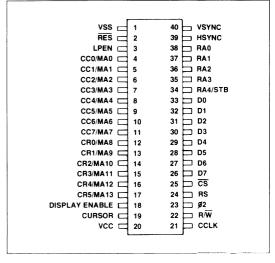

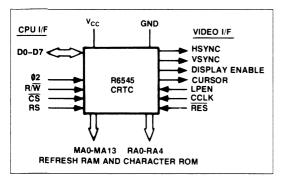

|     | R6545 CRT Controller (CRTC)                     |       |   | R6500/42 One-Chip Intelligent Peripheral                         |       |

|     | R6545-1 CRT Controller (CRTC)                   |       |   | Controller                                                       |       |

|     | R6549 Color Video Display Generator (CVDG)      | 2-134 |   | R65/41EB Backpack Emulator                                       |       |

|     | R6551 Asynchronous Communications Interface     | 0.405 |   | R65/41EAB Backpack Emulator                                      | 3-253 |

|     | Adapter (ACIA)                                  |       |   | R6541Q One-Chip Intelligent Peripheral                           |       |

|     | R6592 Single Chip Printer Controller            | 2-185 |   | Controller                                                       | 3-258 |

|     | R65560 Multi-Protocol Communications Controller | 0.100 |   | R6500/43 One-Chip Intelligent Peripheral                         | 0.055 |

|     | (MPCC)                                          | 2-196 |   | Controller                                                       | 3-258 |

# **TABLE OF CONTENTS (Continued)**

| 4 | Memory Products                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-1   |     | RDC-1024 Rockwell Design Center 8K/32K/64K     |         |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------------------------------------------------|---------|

|   | Product Family Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-2   |     | Target RAM Module                              | 6-26    |

|   | Masked ROMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |     | RDC-1030 Multiple Target Development System    |         |

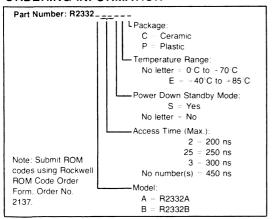

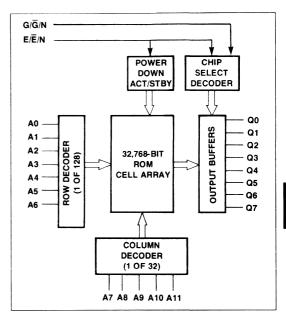

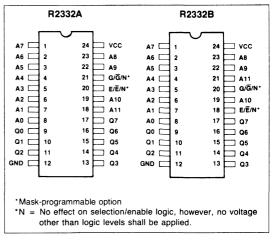

|   | R2332A 32K NMOS Static ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-3   |     | PROM Programmer Module                         | 6-30    |

|   | R2332B 32K NMOS Static ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-3   |     | Software Preparation System                    |         |

|   | R2364A 64K NMOS Static ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-7   |     | SPS-200 Software Preparation System Peripheral |         |

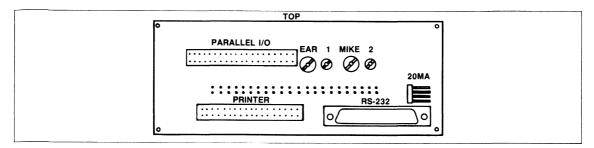

|   | R2364B 64K NMOS Static ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-11  |     | Connector Module                               | 6-36    |

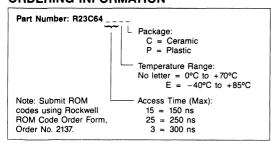

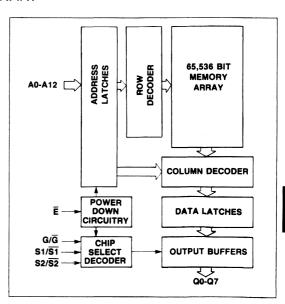

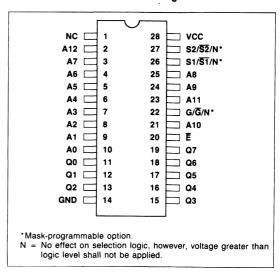

|   | R23C64 64K CMOS Static ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-15  |     |                                                |         |

|   | R23128 128K NMOS Static ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-19  | 7   | Integral Modems                                | 7-1     |

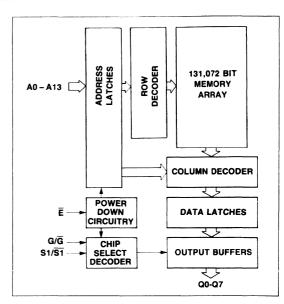

|   | R23C128 128K CMOS ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-23  |     | Product Family Overview                        | 7-2     |

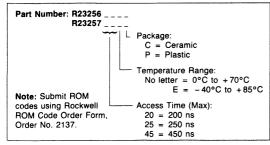

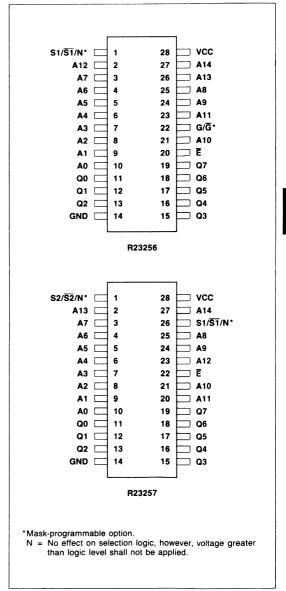

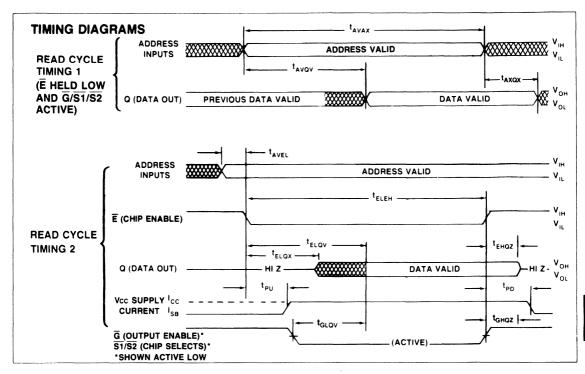

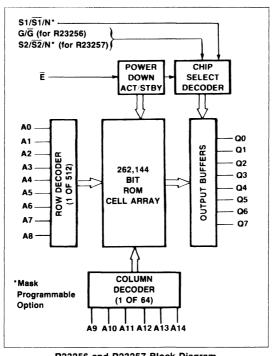

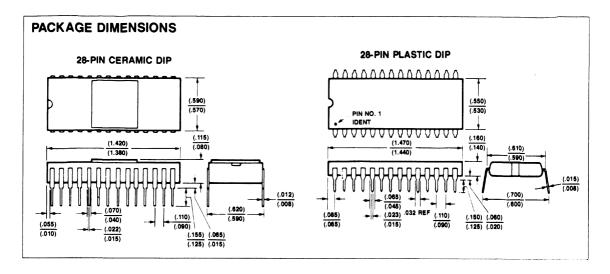

|   | R23256 256K Static ROMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-27  |     | Product Preview—High Speed Modems              |         |

|   | R23257 256K Static ROMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-27  |     | R96FT/SEC 9600 BPS Fast Train Modem with       |         |

|   | UV Erasable PROMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |     | Secondary Channel                              | 7-3     |

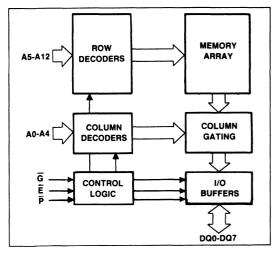

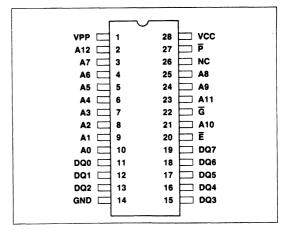

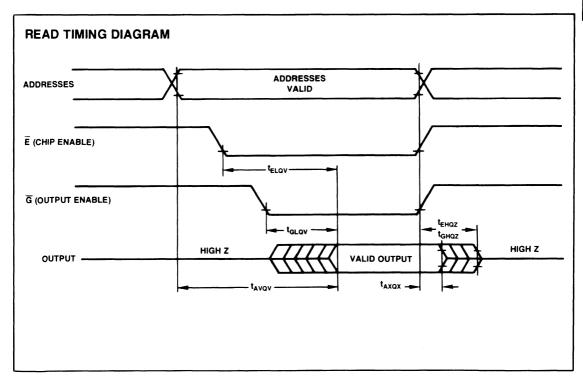

|   | R87C64 64K CMOS UV EPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-31  |     | R144 Synchronous 14.4 KBPS Modem               | 7-4     |

|   | TIO/OUT DIRECTION OF THE PROPERTY OF THE PROPE |       |     | R4875 4800/75 BPS Modem                        | 7-5     |

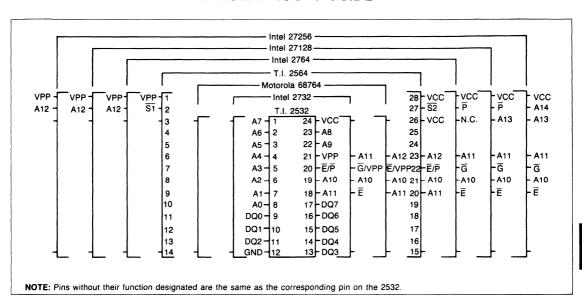

|   | EPROM Pinouts Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-37  |     | R208A/B 4800 BPS Modem                         | 7-6     |

|   | El Hom I modis dalde                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |     | High Speed                                     |         |

| 5 | Intelligent Display Controllers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-1   |     | R96FAX 9600 BPS Facsimile Modem                | 7-7     |

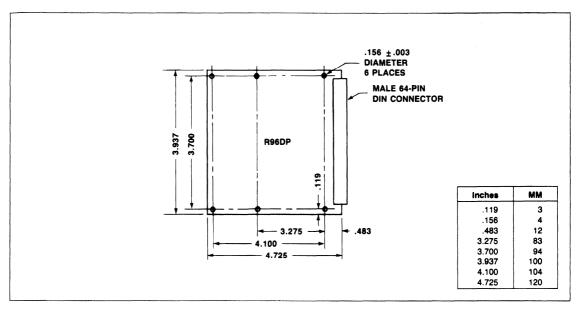

| 3 | Product Family Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-2   |     | R96DP 9600 BPS Data Pump Modem                 | 7-20    |

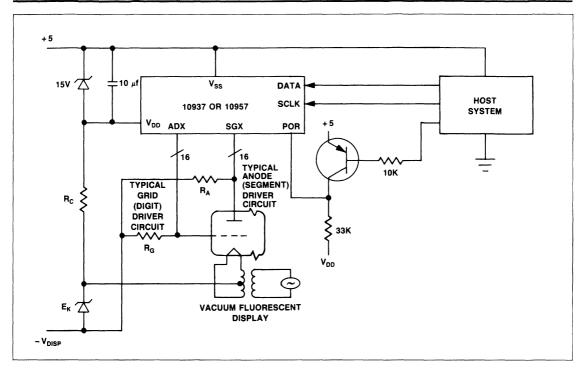

|   | 10937 Alphanumeric Display Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-3   |     | R96FT 9600 BPS Fast Train Modem                | 7-34    |

|   | 10957 Alphanumeric Display Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-3   |     | V96P/1 9600 BPS Modem                          | 7-47    |

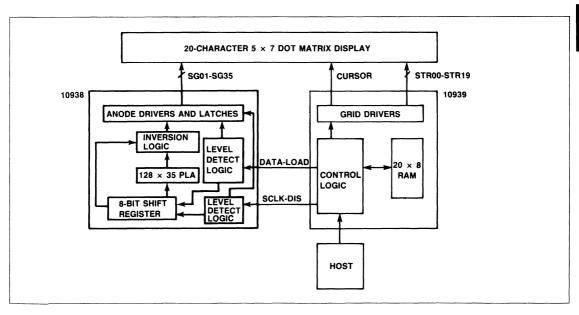

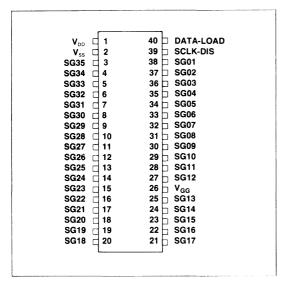

|   | 10938 Dot Matrix Display Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-11  |     | R48DP 4800 BPS Data Pump Modem                 | 7-55    |

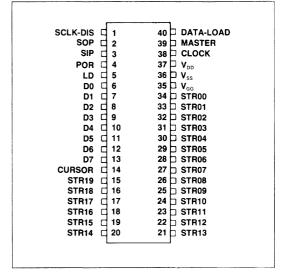

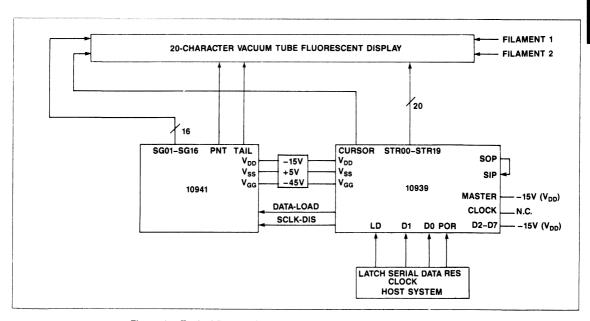

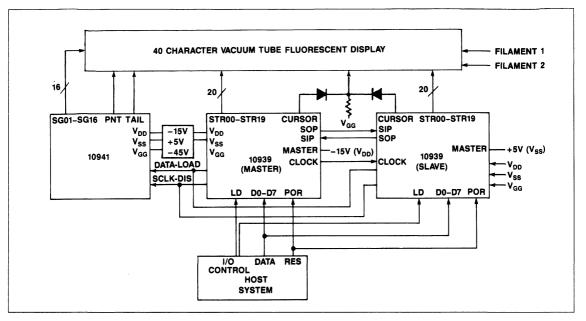

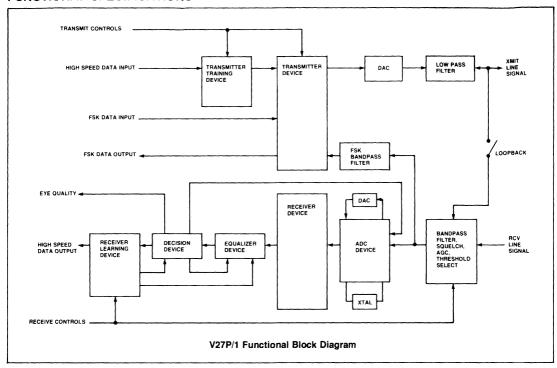

|   | 10939 Dot Matrix Display Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-11  |     | V27P/1 4800 BPS Modem                          | 7-69    |

|   | 10939 Dot Matrix Display Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-21  |     | Product Preview—Low to Medium Speed            |         |

|   | 10942 Dot Matrix Display Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-21  |     | Modems                                         |         |

|   | 10943 Dot Matrix Display Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-21  |     | R1212DS Modem Device Set                       |         |

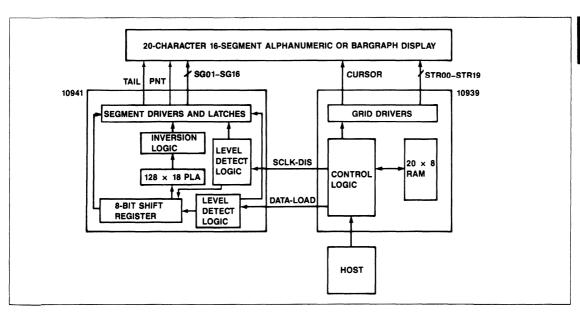

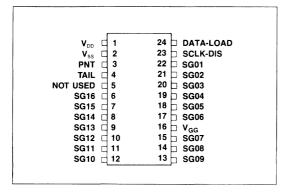

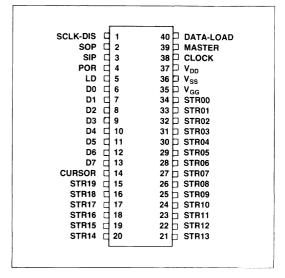

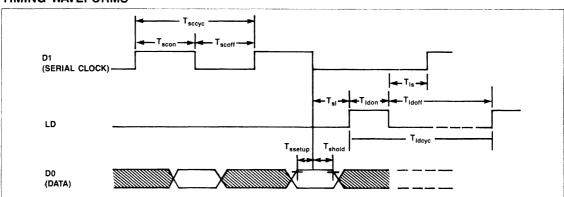

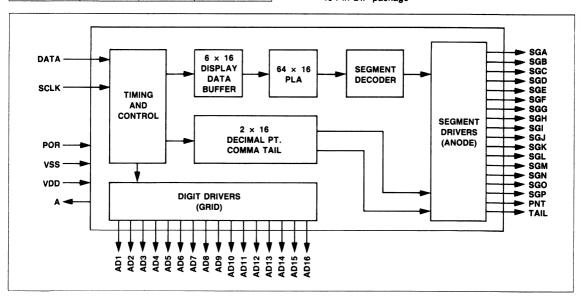

|   | 10941 Alphanumeric and Bargraph Display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | J-21  |     | (212A Compatible)                              | 7-76    |

|   | Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-31  |     | R2424DS Modem Device Set                       |         |

|   | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-31  |     | R24DP 2400 BPS Modem                           |         |

|   | 10939 Alphanumeric and Bargraph Display Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-31  |     | (201C Compatible)                              | 7-78    |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-41  |     | Low to Medium Speed                            |         |

|   | 10951 Bargraph and Numeric Display Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-51  |     | R1212 1200 BPS Full Duplex Modem               | 7-79    |

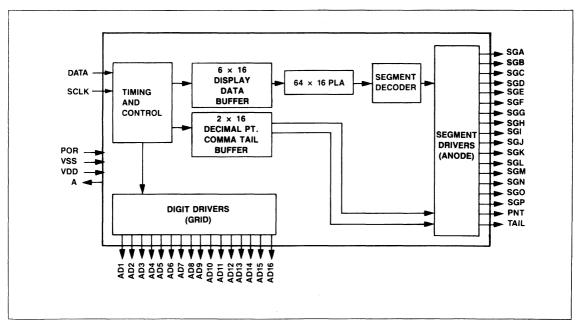

|   | 10955 Segmented Display Controller/Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | J-5 I |     | R1212/U 1200 BPS Full Duplex Modern with       | ,,,     |